UNIDADE CENTRAL DE PROCESSAMENTO PARA APLICAÇÕES GERAIS

por

V. Proano<sup>1</sup>, A. L. Cunha<sup>2</sup>, A. C. A. Mol<sup>3</sup>, F. Schilindwein

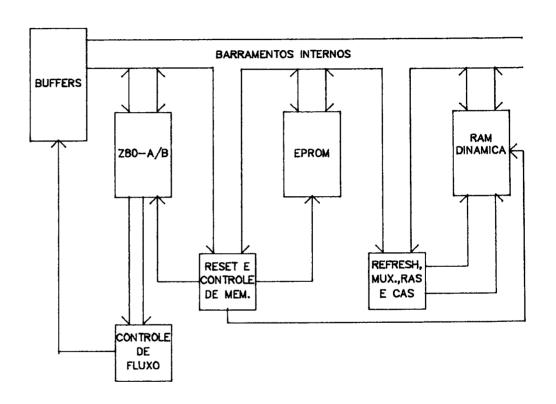

Resumo -- O presente trabalho apresenta o desenvolvimento de um módulo básico de processador e memória para aplicações gerais, o qual é montado em uma única placa com pinagem compatível com o padrão STD. Utilizando o microprocessador Z80, pode trabalhar com relógio de 4 ou 6 MHz. Com 8 Kbytes de EPROM, podendo ser configurado para 4 ou 16 Kbytes, possui também 64 Kbytes de RAM totalmente acessíveis. O circuito inclui uma lógica de reinicialização e outra que permite o acesso direto à memória, DMA, através de um controlador conectado no barramento externo.

# Introdução

Na atualidade, muitos equipamentos (em particular os utilizados na área biomédica) são baseados em microprocessador. Isto resulta, na maioria dos casos, em um equipamento flexível, facilmente adaptável a novas situações de trabalho, preciso e altamente confiável. Utilizando módulos padronizados, somam-se às vantagens anteriores o fato de haver um menor investimento de tempo e dinheiro na fase de desenvolvimento e principalmente na manutenção.

Tendo em mente os aspectos apresentados, desenvolveu-se no Programa de Engenharia Biomédica da COPPE/UFRJ uma Unidade Central de Processamento para Aplicações Gerais, CPU-AG. O objetivo deste módulo é servir de base para o desenvolvimento dos diferentes projetos nos quais torna-se necessária a utilização de um microcomputador dedicado. O projeto foi inspirado no trabalho de Adams, J. (1984).

//Trabalho recebido em 30/5/87 e aceito em 20/10/88//

<sup>1</sup> Casilla 746 Ibarra, Imbabura Ecuador.

<sup>2</sup> Programa de Engenharia Elétrica, COPPE/UFRJ

<sup>3</sup> Departamento de Engenharia Eletrônica, EE/UFRJ

<sup>4</sup> Programa de Engenharia Biomédica, COPPE/UFRJ

# Características

O módulo foi projetado para trabalhar com o microprocessador Z80 e com a memória incluída no mesmo cartão, como já foi menciona do anteriormente. Não foram necessários buffers para conectar as linhas de dados entre o microprocessador e a memória. Isto possibilitou o uso apenas do sinal de leitura, RD, tanto para instruções de leitura como de escrita na memória. Nos outros barramentos internos também não foi necessário o uso de buffers, pois os circuitos conectados nas linhas de saída do Z80 são todos da família 74LSXX e em nenhum caso excedem a capacidade de fan-out do Z80.Para conferir, ver Texas (1979) e Mostek (1982).

O circuito de relógio é baseado em inversores e pode utilizar um cristal de 4 MHz ou de 6 MHz como circuito ressonante Segundo o cristal utilizado o microprocessador será o Z80-A ou o Z80-B, respectivamente.

Como memória são utilizadas 8 pastilhas 4164 (memória dinâmica 64k x 1) com tempo de acesso menor ou igual a 450 nS. Essas memórias são de baixo custo e, por utilizarem a capacidade total de en dereçamento do Z80, dispensam a utilização de codificadores de endereços. O uso de memória dinâmica, implica na multiplexação das linhas de endereços assim como a geração de endereços de refrescamento e essa lógica complementar foi também incluída na placa CPU-AG.

Por serem circuitos de alta escala de integração, as memórias dinâmicas utilizadas tem 8 pinos de endereços ao invés dos 16 que são necessários para acessar às 65536 células de memória. Para o controle de seleção existem 2 pinos, sendo um para habilitação do acesso às linhas (RAS), e o outro para as colunas (CAS). Durante o RAS os 8 bits menos significativos de endereço são recolhidos através dos 8 pinos de endereço e durante o CAS ocorre o mesmo com os 8 bits mais significativos. Internamente, a memória decodifica os 16 bits recolhidos na forma de linhas e colunas. O circuito desenvolvido gera os sinais de RAS e CAS e controla a multiplexação das linhas de endereços, existindo um ajuste para compatibilizar os tempos segundo o relógio que está sendo utilizado. Uma análise detalhada para este tipo de circuito pode ser encontrada no livro de Coffron, J. (1983).

Existem diferentes fabricantes das pastilhas de memória 4164 e em todos os casos estes integrados têm pinagem e características de temporização comuns. No entanto internamente alguns deles são organizados em matrizes de 512 colunas por 128 linhas, e outros em matrizes de 256 colunas por 256 linhas. Para o refrescamento da me mória dinâmica, é necessária então, a geração de 128 ou 256 endere

ços de linhas dependendo do fabricante das pastilhas. O microprocessador Z80 dispõe apenas de 7 bits para endereços de refrescamen to. Por essa razão foi necessário desenvolver uma lógica adicional para gerar o oitavo bit de refrescamento e tornar o módulo compatível com qualquer uma das versões de 4164 encontradas no mercado.

Como EPROM é utilizada a pastilha 2764 que possui uma capacida de de 8 Kbytes, havendo porém a possibilidade de trocá-la por uma 2732 ou 27128, o que significa que a placa pode possuir até 16 Kbytes de capacidade de EPROM. Para isso foi utilizado um soquete de 28 pinos no qual a 2764 pode ser conectada diretamente, ou então o pino 26 pode ser configurado como + 5 V ou Al3 (linha 13 do barramento de endereços), segundo a necessidade de se configurar o sistema para utilizar 4 ou 16 Kbytes de EPROM, respectivamente.

A lógica desse módulo é implementada de tal forma que quando o sistema é ligado, se produz automaticamente um RESET, com tempo su ficiente para apagar a memória. É possível também gerar um RESET manual, usando a linha PBRESET do barramento externo, e nesse caso a memória dinâmica não é apagada. Essa temporização é feita utilizando um monoestável. Utilizando um flip-flop, ativado pelo pulso do RESET, se consegue que após um RESET, qualquer acesso à região inferior da memória (Al5 = 0) se transforme num acesso à EPROM, ficando a RAM desabilitada nessa região.

Após a primeira instrução de E/S, a EPROM fica desativada e a RAM passa a ser totalmente acessível. A Tabela l indica o mapeamento da memória conforme o chaveamento EPROM/RAM.

TABELA 1 - Mapeamento da memória segundo o sinal de RESET e instru cões de E/S

| CONDIÇÃO                                                             | ENDEREÇOS EM HEXADECIMAL |             |

|----------------------------------------------------------------------|--------------------------|-------------|

|                                                                      | ROM                      | RAM         |

| Após o RESET e antes da pri-<br>meira operação de entrada e<br>saída | 0000 - 3FFF              | 8000 - FFFF |

| Após a primeira operação de<br>entrada e saída                       | desativada               | 0000 - FFFF |

Esse tipo de configuração permite que, ao ocorrer um RESET; o programa residente em EPROM passe a ser executado. Na utilização atual, um programa monitor e uma rotina de carga (residentes em EPROM) são carregados em um endereço alto (maior que 8000 H). A

FIGURA 1 ORGANIZAÇÃO DA CPU-AG

execução desse "BOOT" continua com a transferência do controle a essa rotina de carga que em primeiro lugar desativa a EPROM e habilita a região inferior de RAM através de uma instrução de E/S.Este procedimento termina com a carga e execução do monitor no endereço OOOOH.

O restante do circuito mostrado na Figura (1), está relacionado com o barramento externo. Para compatibilizar os sinais deste

módulo com os do padrão STD, são utilizados 5 buffers tri-state e

bidirecionais. Esses buffers são controlados e habilitados por uma

lógica relativamente complexa que leva em consideração todos os

possíveis casos de funcionamento, incluindo DMA e os três níveis

de interrupções permitidos pelo Z80. Estas características fazem

com que este módulo seja apropriado para diversas aplicações em

instrumentação.

No que diz respeito ao software desenvolvido, o monitor foi ba seado no SISDEPUR, um programa desenvolvido no Núcleo de Computação Eletrônica (NCE/UFRJ), e consta de um conjunto de utilitários que visam facilitar e otimizar o uso do hardware implementado. As rotinas nele contidas podem ser utilizadas como suporte a outros módulos, ou podem ser chamadas diretamente pelo usuário através de uma interface serial, com comandos específicos, como pode ser observado na tela do sistema mostrado na Figura (2).

## < MONITOR >

#### COMANDOS DISPONIVEIS:

| Α  | - ALTERA MEMORIA                     |

|----|--------------------------------------|

| L  | - LISTA 16 BYTES DE MEMORIA          |

| S  | - LISTA 10 LINHAS DE MEMORIA         |

| I  | - CARREGA UM PROGRAMA NA MEMORIA     |

| T  | - TRANSFERE ARQUIVOS                 |

| X  | - EXIBE O CONTEUDO DOS REGISTRADORES |

| M  | - SETA ENDERECO DE MEMORIA           |

| P  | - SETA ENDERECO DE EXECUCAO          |

| G  | - DESVIA PARA O ENDERECO DE EXECUCAO |

| E  | - ENCHE UMA AREA DE MEMORIA          |

| R  | - LE STATUS DE UMA PORTA             |

| C  | - CONFIGURA INTERFACE SERIAL         |

| *  | - DESVIA PARA O SISTEMA              |

| H, | - MENU                               |

Figura 2 - Tela do monitor

>

As rotinas do monitor permitem alterar o conteúdo dos registra dores do microprocessador a qualquer instante. Para isso, além da memória utilizada para as rotinas propriamente ditas, incluindo as variáveis nelas utilizadas, uma área é destinada a emular os registradores do Z8O, e outra é reservada para a pilha.

Os utilitários em si são rotinas especializadas de escrita e leitura de memória e de acordo com as funções por elas desempenhadas, podem ser consideradas como rotinas relacionadas com registra dores, memória e entrada/saída. Dentre as funções relacionadas com os registradores podem ser citadas as de atualização e exibição de endereços e registradores. As relativas a memória incluem atualização, preenchimento, transferência e exibição de determinada área. As rotinas do último grupo se encarregam de monitorar e escrever em qualquer porta, sendo que aqui devem ser consideradas também as rotinas de interface com o usuário, pois entre elas estão aquelas de conversão de ASCII a binário e vice-versa, as de configuração da interface serial, e de exibição nas diferentes formas.

A utilização destas rotinas como monitor pressupõe o uso da interface serial, e de um terminal ou um computador provido de interface serial e executando um programa de comunicações. Nesse caso o programa pode ser visto como uma monitoração contínua da interface serial. No caso de existir um comando válido, prepara a chamada da rotina correspondente, executa e volta ao "loop" de monitoração. O programa permite também mudar de ambiente no caso de existirem diferentes ambientes de usuário, ou então executar uma rotina localizada em qualquer região da memória.

Para a comunicação propriamente dita existem basicamente duas rotinas, CONIN para entrada e CONOUT para saída de informação. Cada uma destas rotinas, antes da instrução de E/S, monitora e controla o estado das linhas de MODEM e dos buffers de transmissão e recepção. Dessa forma a comunicação atinge um alto grau de confiabilidade. A comunicação é bidirecional e "full-duplex", porém para facilitar a transferência de grande quantidade de caracteres (ASCII ou binário) foram implementadas rotinas especializadas que suportam o protocolo XON/XOFF.

## Resultados

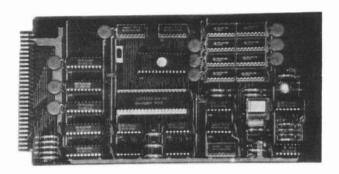

Inicialmente o circuito foi montado numa placa usando a técnica de wire-wrapping. Atualmente o laboratório dispõe de placas de circuito impresso, o que torna a CPU-AG facilmente reproduzível. A Figura (3) é uma fotografia desta placa.

Após testes estáticos, se realizaram testes dos circuitos de relógio, de habitação da EPROM, de multiplexação de endereços, e de refrescamento. Finalmente foi testado o controle e fluxo do bar ramento externo. Para a realização dos testes foram gravadas peque nas rotinas em EPROM, e se utilizou um osciloscópio para conferir a temporização dos sinais. Nos testes mais complexos, um analisdor de estados lógicos foi também muito útil.

Figura 3 - Circuito impresso da CPU-AG

Posteriormente foi montada uma interface serial e implementado um monitor. Com isso, e o fato de que a RAM fica totalmente acessível, foi possível que o módulo pudesse ser utilizado como seu próprio sistema de desenvolvimento. Para tanto, utilizou-se um outro computador como terminal, conectado através da interface serial.

Para interagir com o sistema desenvolvido inicialmente se utilizou um microcomputador SDE45 com um programa chamado LINKB45 pas sando-se depois a utilizar um microcomputador UNITRON juntamente com o programa COM, nos dois casos em ambiente CP/M. A vantagem de utilizar um microcomputador como terminal está no fato de aproveitar as facilidades do computador como o console, facilidades de armazenamento, e etc.

Atualmente este módulo está sendo utilizado no sistema computa dorizado para o mapeamento do campo ultra-sônico desenvolvido no PEB-COPPE/UFRJ, no sistema rápido de aquisição e exibição de sinais que está em fase de desenvolvimento também no PEB e como CPU de um microcomputador com sistema operacional de disco compatível

com CP/M que está sendo desenvolvido no Departamento de Eletrônica da Escola de Engenharia da UFRJ.

## Agradecimentos

Os autores agradecem ao CNPq e à FINEP pelo apoio financeiro, aos Profs. João Carlos Machado e Antônio Cláudio Gómez de Sousa pelo apoio para a execução deste projeto, a José Mauro Teixeira e demais membros dos laboratórios de microprocessadores e ultra-som do PEB, pela gravação das EPROM e pela colaboração nas diferentes fases do desenvolvimento.

# Bibliografia

- (1) ADAMS, J. H. "SC84 Microcomputer", Wireless World, nº 5, pp. 37-51, (1984).

- (2) COFFRON, J. W. "Z80 Applications", Sybex (1983).

- (3) MOSTEK CORPORATION "Microeletronic Data Book", (1982).

- (4) TEXAS INSTRUMENTS CORP. "The TTL Data Book for Design Engineers", (1979).

## CENTRAL PROCESSING UNIT FOR GENERAL APPLICATIONS

Abstract -- This work describes the development of a memory and processor module. It is intended for general applications and the external bus is compatible with the STD standard. This module uses the Z80 microprocessor, being able to run using a 4 or 6 MHz clock. It has an 8 Kbyte EPROM, which can be replaced by a 4 or 16 Kbyte one, and also has a 64 Kbyte fully accessible RAM. The circuit includes a RESET logic, a clock generator and buffers which allows Direct Memory access through an external DMA controller.